Vhdl Code For Serial Adder Using Finite State Machine

Vhdl Code For Serial Adder Using Fsm ->>->>->>DOWNLOAD. Sequence detector ' using FSM(Finite State Machine) in VHDL. Meadow Vista Apartments Weatherford Tx. Serial In Parallel Out Shift. I'm trying to implement VHDL code using Finite state machine and Port mapping to components Does any one have an idea how to do it, since it isn't allowed to include.

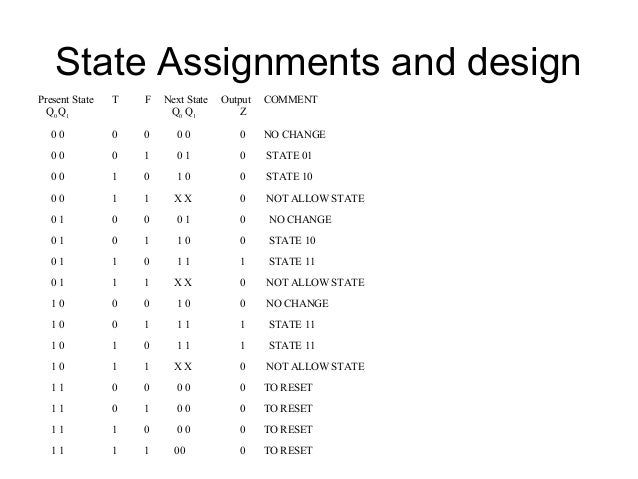

I'm trying to write some vhdl that detects a given pattern in a string of bits. The circuit should output 1 when it finds the pattern '110' in the input stream. My input is 'X' and my output is 'Z'.

For some reason when I simulate the results, I'm not getting any output for 'Z'. It just stays low. This is what I have so far: library IEEE; use IEEE.STD_LOGIC_1164.ALL; entity checker is Port ( clk: in STD_LOGIC; x: in STD_LOGIC; z: out STD_LOGIC); end checker; architecture Behavioral of checker is type state_type is (S0, S1, S2); signal pr_state: state_type:= S0; signal nx_state: state_type:= S0; begin process(clk) begin if (rising_edge(clk)) then pr_state z z z z clk, x =>x, z =>z ); -- Clock process definitions clk_process:process begin clk. There are several issues with your code. My rewritten version is below. Gta Vice City Bomb Blast Game. The main problem is that your code was that the assignment of Z was incorrect.

The next problem was that the state machine itself was incorrect. As it was written, Z should have gone high after a pattern of '11', and not '110'. It also would have gotten stuck in state S2 and not recovered. I should also mention that there were several 'stylistic' issues with your code too. Having two processes instead of one was a major one. I cleaned up that as well.

This allowed for having only a single state signal, which makes the whole thing more readable as well. Library IEEE; use IEEE.STD_LOGIC_1164.ALL; entity checker is Port ( clk: in STD_LOGIC; x: in STD_LOGIC; z: out STD_LOGIC); end checker; architecture Behavioral of checker is type state_type is (S0, S1, S2); signal state: state_type:= S0; begin process(clk) begin if rising_edge(clk) then case state is when S0 =>z z if x = '0' then state z.

Comments are closed.